FPGAs (field programmable gate arrays) are increasing in popularity due to their flexibility and adaptability in various applications such as signal processing, machine learning, and networking. However, programming FPGAs can be difficult due to the low-level hardware description languages required.

Traditional FPGA development requires expertise in hardware description languages such as Verilog and/or VHDL. These languages differ from the high-level programming languages which are familiar to software engineers.

The complexity of FPGA architectures adds another layer of difficulty. Designers must understand the underlying hardware elements, such as logic blocks, routing resources, and timing constraints, to effectively utilize the FPGA's capabilities.

High-level synthesis offers a solution by filling the gap between software and hardware design. It makes FPGA programming more accessible and efficient for a broader range of developers.

What is High-Level Synthesis?

High-level synthesis is a process that translates code in high-level programming languages into RTL (register-transfer level) descriptions suitable for FPGA implementation. It connects the software and hardware design, allowing developers to focus on algorithmic aspects rather than low-level hardware details.

How does High-Level Synthesis work?

High-level synthesis works by analyzing high-level code and generating equivalent RTL descriptions. This involves tasks such as algorithm partitioning, scheduling, resource allocation, and RTL generation. HLS tools use optimization techniques such as pipelining and parallelization to improve performance, minimize resource utilization, and meet timing constraints.

Tools like Vitis from Xilinx or Intel's HLS Compiler provide comprehensive HLS capabilities, supporting languages like C as input.

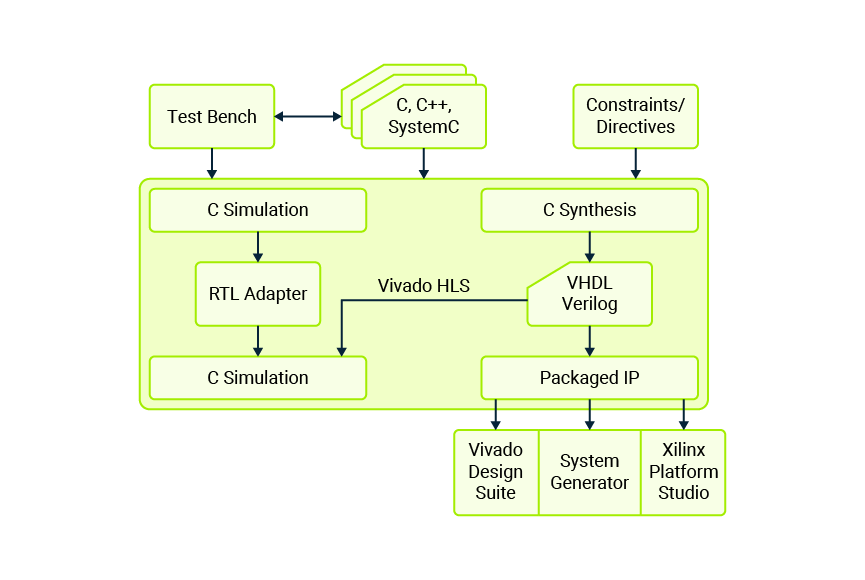

Vitis HLS, tailored for Xilinx products, serves as a high-level synthesis tool. Previously known as Vivado HLS, the terms may appear interchangeably, as much of the documentation for Vitis HLS draws from materials initially crafted for Vivado HLS.

The figure below shows the Vivado HLS design flow.

How to use High-Level Synthesis?

The most common inputs for high-level synthesis are standard C, but nowadays, we may also use code in Python and even more dedicated languages such as P4.

C source as HLS input

For example, let's try to prepare a simple signal forwarder. Its output shall reflect the input value. A description in C could look like the following:

bool test_led(bool sw) {

return sw;

}

As this is quite a simple example, HLS tools may need additional information to recognize the inputs and outputs properly. To keep the functionality of C sources, additional information can be passed by the #pragma directive. The C compiler can be configured to ignore unknown preprocessor directives, and the same source files could be used by either the C compiler or the HLS. Additional pragmas we will use in our example are:

#pragma HLS INTERFACE mode=ap_none port=sw

#pragma HLS INTERFACE mode=ap_none port=return

This will guide the HLS to the variables that shall be considered entity ports. HLS will figure out which are the inputs and outputs by analyzing the variables' relations. Furthermore, pragmas may provide additional guidelines for HLS to generate appropriate RTL hardware design.

Our code after putting everything together:

bool test_led(bool sw) {

#pragma HLS INTERFACE mode=ap_none port=sw

#pragma HLS INTERFACE mode=ap_none port=return

return sw;

}

As a result of high-level synthesis, we get the following HDL output:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity test_led is

port (

sw : IN STD_LOGIC;

led : OUT STD_LOGIC );

end;

architecture behav of test_led is

attribute CORE_GENERATION_INFO : STRING;

attribute CORE_GENERATION_INFO of behav : architecture is

"test_led_test_led,hls_ip_2021_2,{HLS_INPUT_TYPE=cxx,HLS_INPUT_FLOAT=0,HLS_INPUT_FIXED=0,HLS_INPUT_PART=xc7vh580t-hcg1931-1,HLS_INPUT_CLOCK=10.000000,HLS_INPUT_ARCH=others,HLS_SYN_CLOCK=0.000000,HLS_SYN_LAT=0,HLS_SYN_TPT=none,HLS_SYN_MEM=0,HLS_SYN_DSP=0,HLS_SYN_FF=0,HLS_SYN_LUT=0,HLS_VERSION=2021_2}";

begin

led <= sw;

end behav;

P4 as HLS input

HLS uses the C language as an input for hardware block generation, but other initiatives use more specialized solutions, like the P4 language.

P4 is a domain-specific language designed for specifying packet processing algorithms. It's typically used in networking hardware, such as switches and routers.

A P4 program defines how incoming packets should be processed, including actions such as parsing headers, performing lookups, updating packet headers, and forwarding packets. HLS tools can take a P4 program as input and transform it into hardware description language code.

Python as HLS input

LiteX is a Python library for hardware description that allows the description of digital hardware using Python syntax, which is familiar to many developers. This makes it easier to express complex digital designs using a high-level language, reducing the learning curve associated with traditional HDLs. Generated Verilog or VHDL sources allow for synthesis using traditional electronic design automation tools like Vivado or Quartus.

Benefits of using HLS

HLS accelerates FPGA development by allowing designers to prepare complex algorithms and functionalities in high-level programming languages. This abstraction level enables faster prototyping and iteration compared to traditional hardware description languages. Designers can focus on algorithmic optimizations and functionality rather than low-level hardware details.

Designers can iterate through different algorithmic implementations, adjusting parameters and configurations to achieve the desired performance, resource utilization, and power efficiency. This is particularly valuable in applications where algorithmic improvement is critical, such as digital signal processing, image processing, and machine learning.

HLS tools support a wide range of high-level programming languages, enabling designers to use their existing software skills and libraries. C-based HLS tools, for example, allow developers to reuse the existing C/C++ codebase, libraries, and frameworks, reducing the time to market. HLS tools also support industry-standard interfaces and protocols, facilitating integration with existing software and hardware ecosystems.

HLS promotes system-level design by enabling designers to model and optimize entire systems at a higher level of abstraction. Rather than focusing on individual hardware components, designers can design and optimize system-level architectures, including multiple processing elements, memory hierarchies, and communication interfaces.

Leading FPGA vendors offer comprehensive HLS toolchains, such as Xilinx's Vitis HLS and Intel's HLS Compiler. These tools provide a unified development environment for HLS design, synthesis, optimization, and verification.HLS tools integrate with existing FPGA design flows, enabling designers to use familiar workflows and methodologies. HLS tools also offer advanced optimization techniques to maximize performance and resource utilization, including pipelining, loop unrolling, and resource sharing.

Summary

High-level synthesis enables developers to express complex algorithms and functionalities in high-level programming languages, making FPGA development more accessible to a broader range of designers, including software engineers.

HLS tools provide comprehensive synthesis, optimization, and verification capabilities, enabling designers to achieve high-performance hardware implementations while minimizing resource utilization and meeting timing constraints. The integration of HLS into the FPGA design flow allows designers to focus on algorithmic refinements and functionality rather than low-level hardware design.

HLS promotes algorithm exploration, system-level design, and code reuse.

High-level synthesis offers an efficient approach to FPGA design. With tools like Xilinx's Vitis and Intel HLS Compiler, designers can overcome hardware design challenges, accelerate time to market, and deliver high-performance FPGA-based solutions that address the evolving demands of today's computational workloads.

Must read literature on HLS

- High-Level Synthesis Blue Book, Michael Fingeroff

- High-Level Synthesis: From Algorithm to Digital Circuit, Adam Morawiec, Philippe Coussy & Giovanni De Micheli

- BSV by Example, Rishiyur S Nikhil & Kathy R Czeck